## An Ultra Broadband GaAs MESFET Preamplifier IC for a 10Gb/s Optical Communication System

*M. Miyashita, K. Maemura, K. Yamamoto, T. Shimura,

M. Nogami\*, K. Motoshima\*, T. Kitayama\*, and Y. Mitsui*

Optoelectronic and Microwave Devices Laboratory

\*Communication Systems Laboratory

Mitsubishi Electric Corporation

4-1, Mizuhara, Itami, Hyogo 664, Japan

\*5-1-1, Ofuna, Kamakura, Kanagawa 247, Japan

### ABSTRACT

An ultra broadband GaAs MESFET preamplifier IC is developed for a 10 Gb/s optical communication system. High transimpedance of 44 dBΩ has been obtained for DC to 12 GHz. A receiver has also been fabricated by using this preamplifier IC and a photodiode. The receiver operates with extremely low equivalent input noise current of 12.6 pA/√Hz for DC to 7.8 GHz. This paper describes circuit design, high frequency characteristics of the preamplifier IC and the receiver.

### INTRODUCTION

Recently, the demand for the high speed and broadband optical communication has been increased. The high speed and broadband IC's have been studied for the fiber-optic application. The transmission rates of these IC's are increased up to 10 Gb/s or more. In order to realize a preamplifier IC which is a key part for fiber-optic application, we adopted the Self-Aligned Gate MESFET (SAGFET). The SAGFET has been developed for high speed GaAs LSI, such as SRAM [1] and gate array [2]. Because of good process controllability, the SAGFET leads to the good uniformity of preamplifier performance.

This paper describes circuit design, high frequency characteristics and superior production controllability of the preamplifier IC.

### CIRCUIT DESIGN

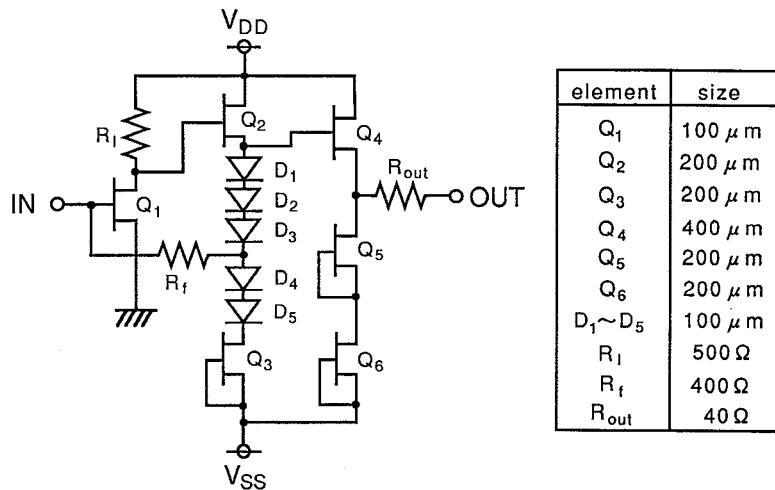

Figure 1 shows the circuit diagram of the IC. Taking account of trade-off between the noise performance and broad band-width, the IC must be designed in

order to get the high feedback resistance ( $R_f$ ) and the low total input capacitance ( $C_t$ ).

Dominant noise sources in the preamplifier are the thermal noise of the input FET and that of feedback resistor.

The equivalent input noise current ( $\overline{in_{FET}^2}$ ) due to the thermal noise of the input FET( $Q_1$ ) is shown as follows [3]

$$\overline{in_{FET}^2} = 4kT\Gamma \frac{(\omega C_t)^2}{g_m} \Delta f \quad \dots(1)$$

where  $\Gamma$  is noise factor [3],  $\Delta f$  is operating band-width,  $k$  is Boltzmann constant,  $T$  is absolute temperature,  $\omega$  is angular frequency, and  $g_m$  is transconductance of the input FET ( $Q_1$ ).  $C_t$  is equal to sum of input gate capacitance ( $C_g$ ) of input FET and parasitic capacitance ( $C_{PD}$ ) of the photodiode . Total input noise current is expressed by  $g_{mu}$  and  $C_{gu}$ .

$$\overline{in_{FET}^2} = 4kT\Gamma \frac{(\omega (C_{PD} + C_{gu} \times W))^2}{g_{mu} \times W} \Delta f \quad \dots(2)$$

where  $g_{mu}$  and  $C_{gu}$  are transconductance and input gate capacitance per unit gate width. We decided the gate width (W) of input FET ( $Q_1$ ) as to get minimum noise current, which is realized at a condition of  $W = C_{PD}/C_{gu}$ .

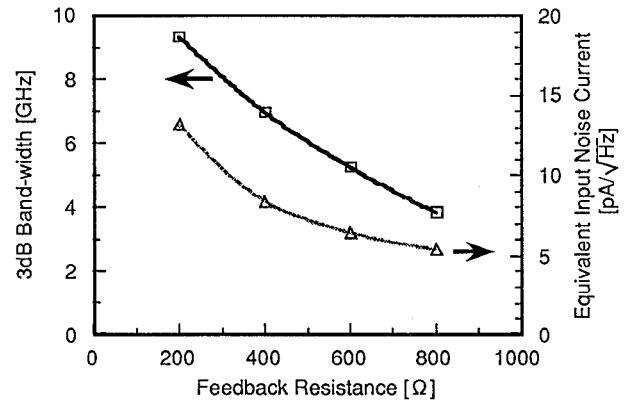

In figure 2, the 3 dB band-width ( $f_{3dB}$ ) and equivalent input noise current ( $\sqrt{\overline{in_t^2}}$ ) in the IC are plotted against feedback resistance ( $R_f$ ). On this design,  $f_{3dB}$  is settled to be about 70 percent of 10 Gb/s and  $R_f$  is determined. Each component is optimized using SPICE with the GaAs MESFET model. In figure

Fig.1 Circuit diagram of the IC.

,  $f_{3\text{dB}}$  of about 7 GHz is obtained at  $R_f$  of 400  $\Omega$ .

The output buffer consists of three FET's ( $Q_4$ ,  $Q_5$ ,  $Q_6$ ) connected in series, considering of the breakdown voltage of each FET of around 7 V. To prevent the reflection at the output port, the output impedance is matched with  $50 \Omega$  load by connecting the resistor  $R_{out}$  to the output terminal. Table 1 shows each FET size and resistance of the IC after optimization.

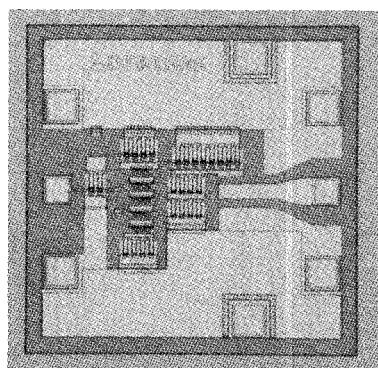

Figure 3 shows the microphotograph of the IC. The FET has a buried p-layer LDD structure (BPLDD) fabricated by a  $0.5\text{ }\mu\text{m}$  self-aligned WSi gate process<sup>[1]</sup>. Because a WSi gate has the high sheet resistance compared with a Au gate, the effect of gate resistance on high frequency operation cannot be neglected and brings about the narrow band-width and the poor noise performance. In order to reduce the gate resistance, the FET is composed of parallel connected short gate finger of  $25\text{ }\mu\text{m}$  width. The distributed gate resistance ( $R_g$ ) is expressed approximately<sup>[4]</sup> as follows:

$$R_g = R_{\square} \times \frac{W_u}{L_g \times N} \times \frac{1}{3} \quad \dots (3)$$

where  $R$  is the sheet resistance of WSi of about  $4 \Omega/\square$ ,  $L_g$  is the gate length of  $0.5 \mu\text{m}$ ,  $W_u$  is unit finger width and  $N$  is the number of the fingers. In the result of fabrication,  $R_g$  is  $17.6 \Omega$  for the input FET( $Q_1$ ) with gate width of  $100 \mu\text{m}$ , which agrees well with a estimated value from the expression (3).

Fig.2 3 dB band-width and equivalent input noise current versus feedback resistance.

Fig.3 Microphotograph of the preamplifier IC.

(The chip size is 0.8 mm x 0.8 mm)

As concerns another device parameters, transconductance ( $g_m$ ) and drain conductance ( $g_d$ ) are 300 mS/mm and 6 mS/mm with standard deviation of 30 mS/mm and 0.7 mS/mm for a 3 inch wafer, respectively. The threshold voltage ( $V_{th}$ ) of the FET is -0.5 V and its standard deviation ( $\sigma V_{th}$ ) is 30 mV.

To simplify on wafer RF measurements, the coplanar structure is employed for the input and output lines and two Metal-Insulator-Metal capacitors are integrated as bypass capacitors for stabilizing the power supplies of +5 V and -5 V. Chip size is 0.8 mm x 0.8 mm.

#### CHARACTERISTICS

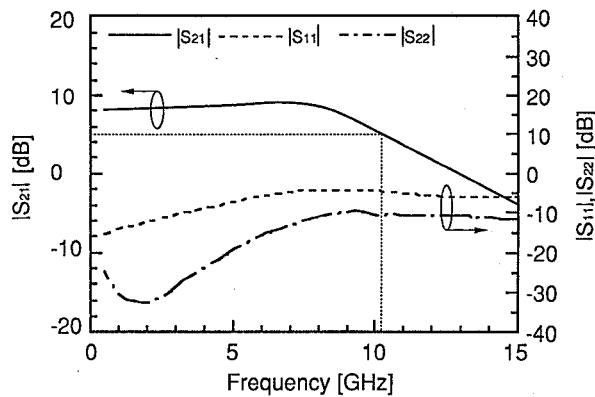

Figure 4 shows the S-parameters of the IC. The high gain  $|S_{21}|$  of 9 dB and the broad band-width over 10 GHz have been obtained. The good matching has also been performed.  $|S_{22}|$  is less than -10 dB for whole frequency range.

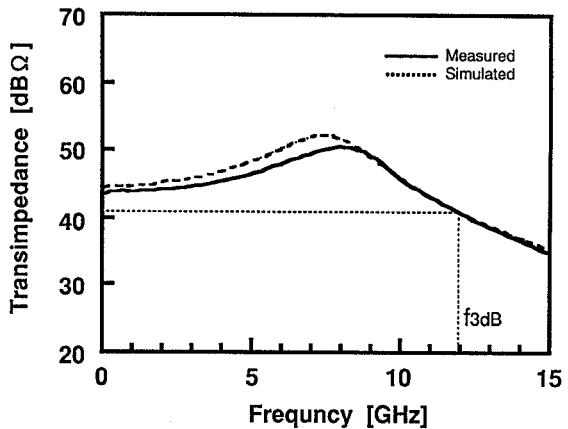

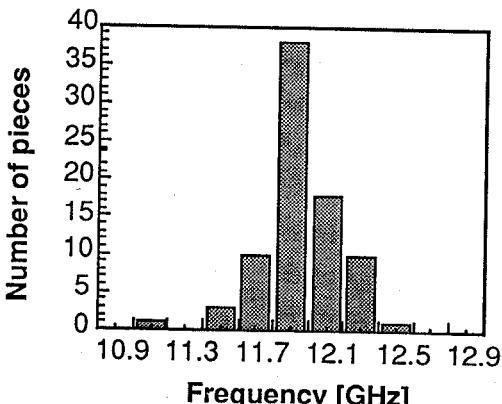

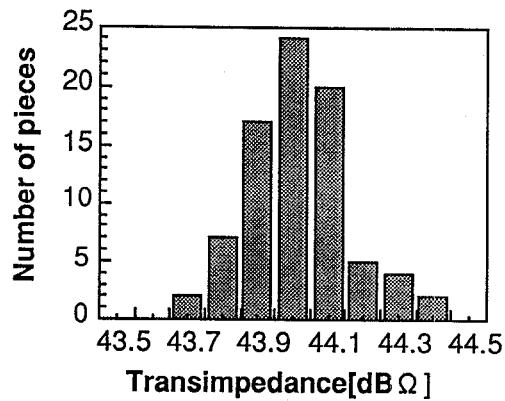

Figure 5 shows the transimpedance characteristics of the IC calculated using S-parameters. The high transimpedance ( $Z_{trans}$ ) of 44 dB $\Omega$  and the excellent broad band-width ( $f_{3dB}$ ) of 12 GHz have been obtained. The results show good agreement with simulation. Figure 6 shows the distribution of  $Z_{trans}$  and  $f_{3dB}$  for a 3 inch wafer. Each standard deviation,  $\sigma Z_{trans}$  and  $\sigma f_{3dB}$ , is as small as 0.2 dB $\Omega$  and 0.2 GHz, respectively. The good uniformity of the preamplifier performance comes from our excellent process controllability.

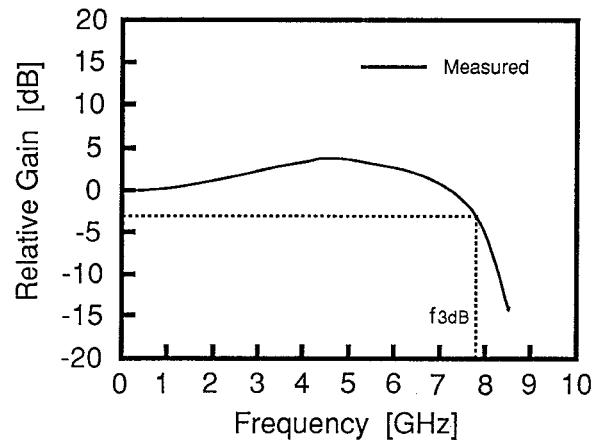

Figure 7 shows frequency response of a receiver consisted of this IC and a pin-photodiode (The over all capacitance of the photodiode is 0.27 pF). The 3dB

Fig.4 S-parameters of the IC.

Fig.5 Transimpedance characteristics of the IC.

Fig.6 Distribution of transimpedance and 3dB band-width.

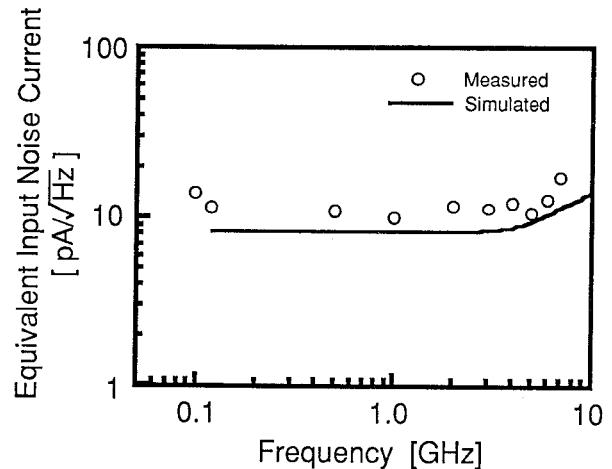

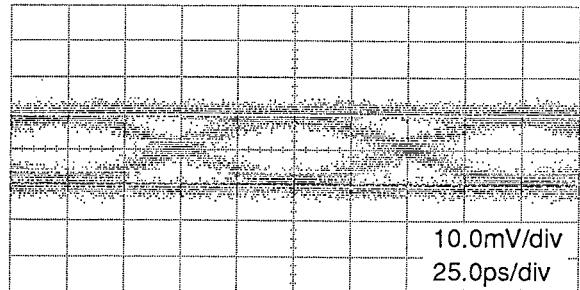

band-width of 7.8 GHz has been obtained, which satisfies our design target. Figure 8 shows noise performance. The equivalent input noise current  $\sqrt{in_t^2}$  higher than  $10\text{ pA}/\sqrt{\text{Hz}}$  has been obtained over the entire frequency range from DC to 7.0 GHz. This indicates superior low noise performance of the IC. Figure 9 shows the pulse response at 10 Gb/s NRZ. Good eye-opening has been observed. The preamplifier IC developed in this work is suitable for the 10 GHz optical communication system.

### CONCLUSION

An ultra broadband preamplifier IC using GaAs MESFETs with  $0.5\text{ }\mu\text{m}$  gate length has been developed for the 10 Gb/s optical communication system. The IC shows high transimpedance of  $44\text{ dB}\Omega$  and broad bandwidth of 12 GHz. For a receiver with this preamplifier IC and a photodiode, broad band-width of 7.8 GHz and low equivalent noise current (average) of  $12.6\text{ pA}/\sqrt{\text{Hz}}$  have been obtained. The preamplifier IC developed in this work is suitable for the 10 Gb/s optical communication.

### ACKNOWLEDGEMENTS

The authors would like to thank Mr. N. Kebukawa for technical assistance, Mr. M. Noda and Mr. Y. Kono for a lot of discussions and suggestions on FET structure, and Dr. M. Otsubo and Dr. K. Ito for their supports and encouragements.

### <Reference>

- [1] M. Noda, et al., "High speed and highly uniform submicron gate BPLDDFET for GaAs LSIs.", Gallium arsenide and related compounds 1989, pp. 653-658.

- [2] N. Higashisaka, et al., "A quasi-complementary-logic GaAs gate array employing air-bridge metallization technology.", IEEE CICC 1991, pp. 14.6.1-14.6.4.

- [3] K. Ogawa, "Noise Caused by GaAs MESFETs in Optical Receivers.", The BELL System Technical Journal, July-August 1981, pp. 923-928.

- [4] P. Wolf, "Microwave Properties of Shottky-barrier Field-effect Transistor.", IBM J. RES. DEVELOP. March 1970, pp. 138-139.

Fig.7 Frequency response of the receiver.

Fig.8 Equivalent input noise current of the receiver.

Fig.9 Pulse response at 10 Gb/s NRZ signals of the receiver.